# **Green Flash: Exascale Computing** on a Petascale Power Budget

John Shalf

David Donofrio, Leonid Oliker, Michael Wehner

National Energy Research Supercomputing Center Lawrence Berkeley National Laboratory

iWAPT Workshop

Tokyo Japan, October 1, 2009

Office of Science

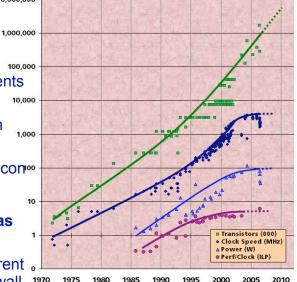

## New Design Constraint: POWER

- Transistors still getting smaller 10,000,000

- Moore's Law is alive and well

- But Dennard scaling is dead!

- No power efficiency improvements with smaller transistors

- No clock frequency scaling with smaller transistors

- All "magical improvement of silicon goodness" has ended

- Cannot continue with business as usual

- DARPA study extrapolated current odesign trends and found brick wall 1970 1975 at end of exponential curves

Olukotun et. al.

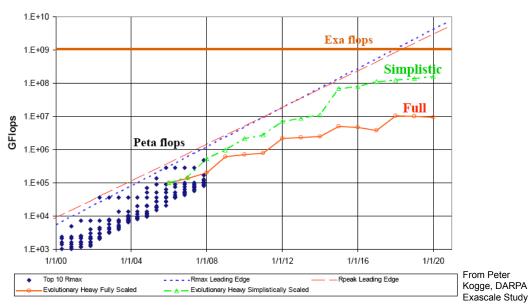

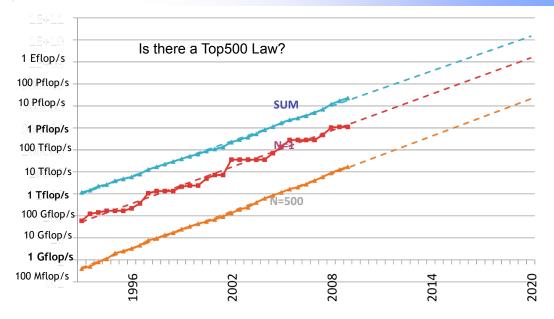

# We won't reach Exaflops with the current approach

# ... and the power costs will still be staggering

From Peter Kogge, DARPA Exascale Study

## Is Exascale a Sure Thing?

## The Challenge

How to get 1000x performance without building a nuclear power plant next to my HPC center?

How do you achieve this in 10 years with a finite development budget?

How do you make it "programmable?"

#### **Green Flash: Overview**

#### We present an alternative approach to developing systems to serve the needs of scientific computing

- Choose our science target first to drive design decisions

- Leverage new technologies driven by consumer market

- Auto-tune software for performance, productivity, and portability

- Use hardware-accelerated architectural emulation to rapidly prototype designs (auto-tune the hardware too!)

- Requires a holistic approach: Must innovate algorithm/software/hardware together (Co-tuning)

## Achieve 100x energy efficiency improvement over mainstream HPC approach

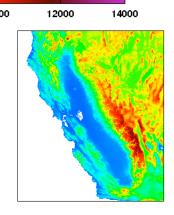

## An Application Driver: Global Cloud Resolving Climate Model

### **Identify Target First!**

(Global Cloud Resolving Climate Model)

Surface Altitude (feet)

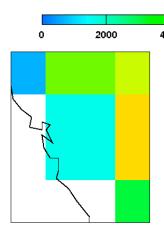

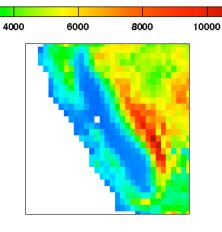

200km Typical resolution of IPCC AR4 models

25km Upper limit of climate models with cloud parameterizations

1km Cloud system resolving models are a transformational change

## Must maintain 1000x faster than real time for practical climate simulation

- ~2 million horizontal subdomains

- 100 Terabytes of Memory

- 5MB memory per subdomain

- ~20 million total subdomains

- 20 PF sustained (200PF peak)

- Nearest-neighbor communication

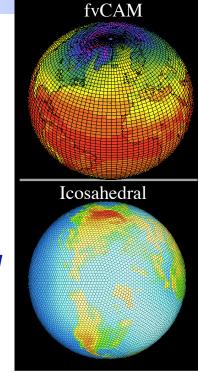

- New discretization for climate model

- CSU Icosahedral Code

## **Energy Efficient Hardware Building Blocks**

Mark Horowitz 2007: "Years of research in low-power embedded computing have shown only one design technique to reduce power: reduce waste."

**Seymour Cray 1977:** "Don't put anything in to a supercomputer that isn't necessary."

### Hardware: What are the problems?

(Lessons from the Berkeley View)

- Current Hardware/Lithography Constraints

- Power limits leading edge chip designs

- Intel Tejas Pentium 4 cancelled due to power issues

- Yield on leading edge processes dropping dramatically

- IBM quotes yields of 10 20% on 8-processor Cell

- Design/validation leading edge chip is becoming unmanageable

- Verification teams > design teams on leading edge processors

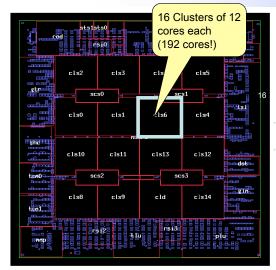

- Solution: Small Is Beautiful

- Simpler (5- to 9-stage pipelined) CPU cores

- · Small cores not much slower than large cores

- Parallel is energy efficient path to performance: CV<sup>2</sup>F

- Lower threshold and supply voltages lowers energy per op

- Redundant processors can improve chip yield

- Cisco Metro 188 CPUs + 4 spares; Sun Niagara sells 6 or 8 CPUs

- Small, regular processing elements easier to verify

Cubic power improvement with lower clock rate due to V<sup>2</sup>F

Slower clock rates enable use of simpler cores

Simpler cores use less area (lower leakage) and reduce cost

Tailor design to application to REDUCE WASTE

This is how iPhones and MP3 players are designed to maximize battery life

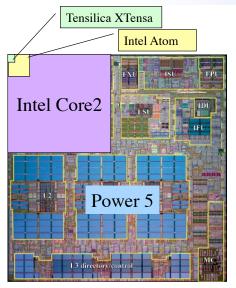

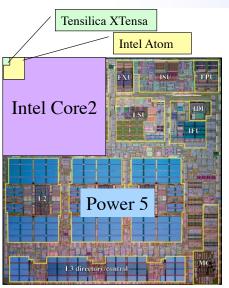

- Power5 (server)

- 120W@1900MHz

- Baseline

- Intel Core2 sc (laptop):

- 15W@1000MHz

- 4x more FLOPs/watt than baseline

- Intel Atom (handhelds)

- 0.625W@800MHz

- 80x more

- Tensilica XTensa DP (Moto Razor) :

- 0.09W@600MHz

- 400x more (80x-120x sustained)

### **Low Power Design Principles**

- Power5 (server)

- 120W@1900MHz

- Baseline

- Intel Core2 sc (laptop):

- 15W@1000MHz

- 4x more FLOPs/watt than baseline

- Intel Atom (handhelds)

- 0.625W@800MHz

- 80x more

- Tensilica XTensa DP (Moto Razor) :

- 0.09W@600MHz

- 400x more (80x-100x sustained)

Even if each simple core is 1/4th as computationally efficient as complex core, you can fit hundreds of them on a single chip and still be 100x more power efficient.

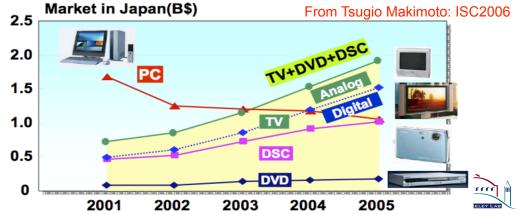

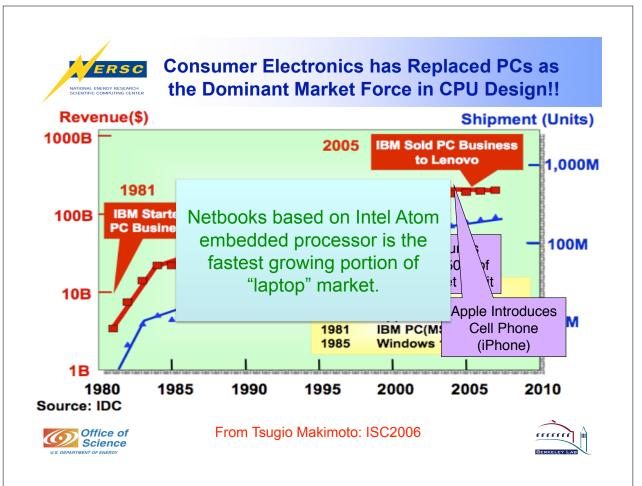

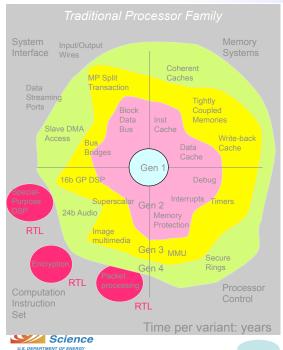

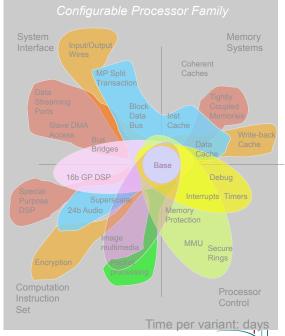

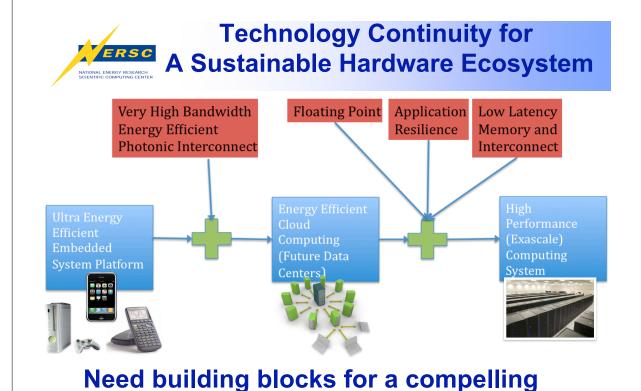

## **Technology Investment Trends**

- 1990s R&D computing hardware dominated by desktop/COTS

- -Had to learn how to use COTS technology for HPC

- 2010 R&D investments moving rapidly to consumer electronics/ embedded processing

- Must learn how to leverage embedded processor technology for future HPC systems

## **Embracing the Embedded Market**

- Have all of the IP and experience with for low-power technology

- Have sophisticated tools for rapid turnaround of designs

- Vibrant commodity market in IP components

- Convergence with HPC requirements

- Need better computational efficiency and lower power

- Now we both must face parallelism

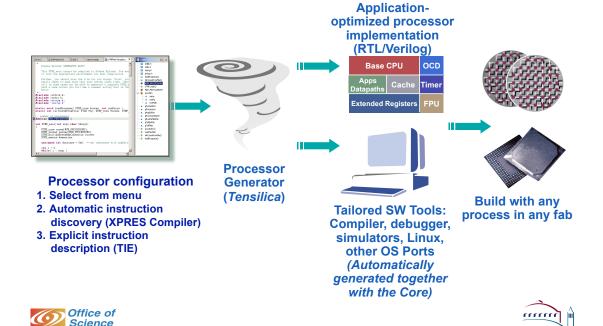

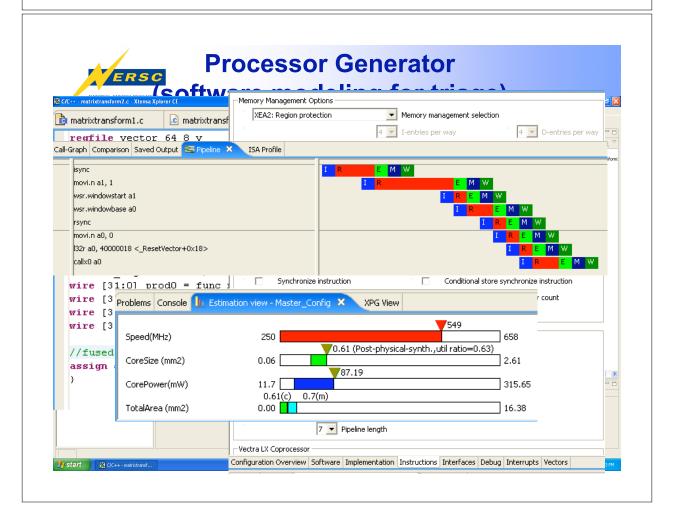

### **Embedded Design Automation**

(Example from Existing Tensilica Design Flow)

- Software Design Space Exploration: "auto-tuning"

- Auto-search through parameter space of code optimizations

- Tune to diverse & complex hardware

- Hardware Design Space Exploration:

- What if hardware configuration was also parameterized?

- Search through diverse space of hardware configurations

- · What if you could do both together?

- Auto-tune software for hardware

- Auto-tune hardware for software

- Repeat?

- Hardware/Software co-design

- Demonstrate how to apply to HPC

- Enable Energy Efficient computing for Extreme Scale Science

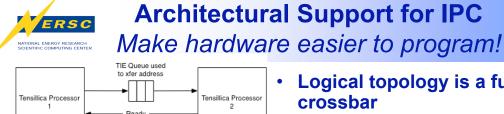

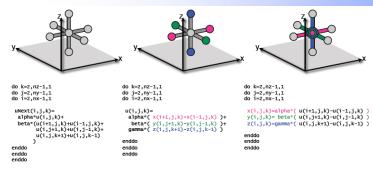

## A Parameterized Core Design To Enable Hardware Auto-Tuning

#### · Highly configurable

- Custom VLIW support

- Configure #registers, width, ISA

- Configure memory subsystem, local-store, cache org

#### Verilog-like TIE language allows custom ISA extensions

- Functional and performance verification built in

- Auto generated compiler intrinsics

- 64-bit IEEE-DP floating point coded up in TIE and available

#### Inter-processor communication easily enabled through:

- TIE Ports

- TIE Queues

- Access to direct HW support for interprocessor communication

- TIE Lookups

- · Allows interface to external ROMs or other RTL block

Area = silicon cost and power

# A Short List of x86 Opcodes that Science Applications Don't Need!

| mnemonic | opl           | op2                    | op3  | op4      | iext | pf 01         | po s | 2 2 P   | eoc s         | nt m                                                                | rl ×   | tested | f modif f | def f   | undef f | f values | description, notes                                           |  |

|----------|---------------|------------------------|------|----------|------|---------------|------|---------|---------------|---------------------------------------------------------------------|--------|--------|-----------|---------|---------|----------|--------------------------------------------------------------|--|

| AAA      | aL            | an                     |      |          |      | $\overline{}$ | 37   | ++      | $\neg$        |                                                                     | $^{-}$ |        | . ossapc  | a.c     | oss.p.  |          | ASCII Adjust After Addition                                  |  |

| AAD      | az            | AN                     |      |          |      | $\vdash$      | D5 0 |         |               |                                                                     | $^{+}$ |        | ossapc    | ss.p.   | 0a.c    |          | ASCII Adjust AX Before Division                              |  |

| AMI      | az            | AH                     |      |          |      |               | D4 0 | 8       |               |                                                                     | $^{+}$ |        | ossapc    | ss.p.   | 0a.c    |          | ASCII Adjust AX After Multiply                               |  |

| AAS      | az.           | an                     |      |          |      |               | 3F   | Ħ       | _             | -11                                                                 | $\top$ |        | . ossapc  | a.c     | 0ss.p.  |          | ASCII Adjust AL After Subtraction                            |  |

| ADC      | x/m8          | z8                     |      |          |      |               | 10   | I       | $\neg$        | -11                                                                 | L      |        | c ossapc  | 0smapc  |         |          | Add with Carry                                               |  |

| ADC      | r/m16/32/64   | z16/32/64              |      |          |      | $\vdash$      | 11   | z       | $\neg$        | -11                                                                 | L      |        | ssapc     | 0smapc  |         |          | Add with Carry                                               |  |

| AD C     | r8            | z/m8                   |      |          |      | $\vdash$      | 12   | z       | $^{-}$        | -11                                                                 | $^{+}$ |        | c ossapc  | 0smapc  |         |          | Add with Carry                                               |  |

| AD C     | r16/32/64     | z/m15/32/64            |      |          |      | $\vdash$      | 13   | z       | $\neg$        | -11                                                                 | $^{+}$ |        | . ossapc  | 0smapc  |         |          | Add with Carry                                               |  |

| AD C     | AL            | inno                   |      |          |      |               | 14   | ++      | $\neg$        | $\neg$                                                              | $^{+}$ |        | c ossapc  | 0smapc  |         |          | Add with Carry                                               |  |

| AD C     | xXX           | imm16/32               |      |          |      | $\vdash$      | 15   | $^{++}$ | $\dashv$      | -11                                                                 | +      |        | c ossapc  | ossapc  |         |          | ôdd with Carry                                               |  |

| ADC      | x/m8          | inm8                   |      |          |      | $\vdash$      | 80   | 2       | $\dashv$      | -11                                                                 | L      |        | cossapc   | 0smapc  |         |          | ådd with Carry                                               |  |

| ADC      | r/m16/32/64   | imm16/32               |      |          |      | $\vdash$      | 81   | 2       | $\dashv$      | -11                                                                 | L      |        | ssapc     | 0smapc  |         |          | Add with Carry                                               |  |

| AD C     | r/m8          | inm8                   |      | _        |      | $\vdash$      | 82   | 2       | _             |                                                                     | L      |        | c ossapc  | 0smapc  |         |          | Add with Carry                                               |  |

| AD C     | r/m16/32/64   | imm8                   |      |          |      | $\vdash$      | 83   | 2       | $\rightarrow$ |                                                                     | L      |        | sapc      | 0smapc  |         |          | Add with Carry                                               |  |

|          |               | zô                     |      | _        |      |               | 00   | z z     | $\rightarrow$ |                                                                     | L      |        | 0ssapc    | 0ssapc  |         |          | 844                                                          |  |

| ADD      |               | x16/32/64              |      | 1        |      | $\vdash$      | 01   | 1       | +             | $\dashv$                                                            | 1.     |        | 0ssapc    | 0ssapc  |         |          | 844                                                          |  |

|          |               | z/168                  |      | <b>!</b> |      | H             | 02   | 1       | +             |                                                                     | Ť      |        | ossapc    | ossapc  |         |          | 844                                                          |  |

| ADD      |               | r/m16/32/64            |      |          |      | $\vdash$      | 03   | 1.      | +             |                                                                     | +      |        | ossapc    | ossapc  |         |          | ådd.                                                         |  |

|          | AL            | inm8                   |      | _        |      | $\vdash$      | 04   | ++      | +             | -                                                                   | +      | _      | 0ssapc    | ossapc  | _       |          | Add                                                          |  |

| ADD      | zAX           | inm16/32               |      | _        |      | $\vdash$      | 0.5  | ++      | $\rightarrow$ |                                                                     | +      | _      | 0ssapc    | 0smapc  | _       |          | A44                                                          |  |

| ADD      | r/m0          | inge8                  |      | _        | _    | $\vdash$      | 80   | 0       | +             |                                                                     | -      | _      | 0ssapc    | 0ssapc  |         |          | 844                                                          |  |

| ADD      | r/m16/32/64   | ings16/32              |      | -        | _    | $\vdash$      | 81   | 0       | -             |                                                                     |        | -      | 0ssapc    | 0ssapc  | _       | _        | 844                                                          |  |

| ADD      | r/m8          | inmes                  |      | -        |      | $\vdash$      | 82   | 0       | +             | $\dashv$                                                            | - 1    | -      | 0ssapc    | ossapc  | -       |          | 844                                                          |  |

| ADD      | r/m16/32/64   | inm8                   |      | -        |      | $\vdash$      | 83   | 0       | +             | +                                                                   | 1      | -      | ossapc    | ossapc  | -       |          | ådd                                                          |  |

| ADDPD    |               | mmm/m128               |      | -        | 5562 | 66 01         |      | z P     |               |                                                                     | - 1    | -      | 0ssapc    | 0 эварс | -       |          | idd Packed Double-FP Values                                  |  |

| ADDPS    | xuu.          | nmy mile               |      | -        | ssez |               | 58   | z P     |               | +                                                                   | +      |        |           |         |         |          | add Packed Single-TP Values                                  |  |

| ADDED    | xour.         | numy mago              |      | -        | 5562 | F2 01         |      | z P     |               |                                                                     | +      | -      |           |         | _       | _        | add Scalar Double-FP Values                                  |  |

| ADDSS    | xnm.          | nany mp 4<br>nany mara |      | -        | 5562 | F2 01         |      | z P     |               |                                                                     | +      | _      |           |         |         |          | Add Scalar Double-IP Values                                  |  |

| ADDSUBPD | xonn.         | nmy m32<br>nm/m128     |      | -        | 5563 | 66 01         |      | I P     | _             |                                                                     | +      | _      | -         |         | _       | -        | ndd Scalar Single-IP Values<br>Packed Double-IP Add/Subtract |  |

| ADDSUBPS | xonn.         | nmmy miles             |      | -        | 5563 |               | 00   | I P     |               |                                                                     | +      |        |           |         |         |          | Packed Double-IP Add/Subtract Packed Single-IP Add/Subtract  |  |

|          |               | NAMA MTSO              |      | _        | sses | 12 0.         | DS   | I P     | 4++           |                                                                     | +      | -      |           |         | -       | _        | * *                                                          |  |

|          | a.c.          | A.K                    | imm8 |          |      | _             | DS   | ++      | +             | .                                                                   | +      | -      | ossapc    | ss.p.   | 0a.c    |          | Adjust AX Before Division                                    |  |

| ALTER    |               |                        |      |          |      | 64            |      | P       | ⊈+ υ          | 1                                                                   | _      |        |           |         |         |          | Alternating branch prefix (used only with Jcc instructions)  |  |

|          |               | an                     | imm8 |          |      |               | D4   | Ш       |               | Ш                                                                   |        |        | ossapc    | ss.p.   | 0a.c    |          | ådjust åX åfter Multiply                                     |  |

|          |               | z8                     |      |          |      |               | 20   | I       |               | Ш                                                                   | L      |        | ossapc    | 0ss.pc  |         |          | Logical AMD                                                  |  |

| AND      |               | z16/32/64              |      |          |      |               | 21   | I       |               |                                                                     | L      |        | ossapc    | 0ss.pc  | a       |          | Logical AND                                                  |  |

|          |               | z/m8                   |      |          |      |               | 22   | I       |               | $\perp \! \! \! \! \! \! \! \! \perp \! \! \! \! \! \! \! \! \! \!$ |        |        | osmapc    | 0sm.pc  | a       | 0        | Logical AND                                                  |  |

| AND      |               | r/m15/32/54            |      |          |      |               | 23   | I       |               | $\Box$                                                              |        |        | osmapc    | 0sm.pc  | a       | oc       | Logical AND                                                  |  |

|          | AL            | imm8                   |      |          |      |               | 24   | $\perp$ |               |                                                                     |        |        | ossapc    | 0sm.pc  | a       | 0c       | Logical AND                                                  |  |

|          | zAX           | imm15/32               |      |          |      |               | 2.5  | IΤ      |               |                                                                     |        |        | ossapc    | 0ss.pc  |         | 0        | Logical AND                                                  |  |

|          | r/m8          | imm8                   |      |          |      |               | 80   | 4       | $\perp$       | ЩТ                                                                  | L      |        | ossapc    | 0ss.pc  |         | 0        | Logical AND                                                  |  |

|          | r/m16/32/64   | imm16/32               |      |          |      |               | 81   | 4       | Т             |                                                                     | L      |        | ossapc    | 0sm.pc  | a       | oc       | Logical AND                                                  |  |

| AND      | r/m8          | imm8                   |      |          |      |               | 82   | 4       |               |                                                                     | L      |        | osmapc    | 0sm.pc  |         | oc       | Logical AND                                                  |  |

| AND      | r/m16/32/64   | imm8                   |      |          |      |               | 83   | 40      | 3+            | П                                                                   | L      |        | osmapc    | 0sm.pc  | a       | oc       | Logical AND                                                  |  |

| ANDNPD   | жит           | mm/m128                |      |          | 5562 | 66 01         | 55   | z P     | 4+            | $\neg \neg$                                                         | T      |        |           |         |         |          | Bitwise Logical AMD NOT of Packed Double-FP Values           |  |

| ANDERPS  | жит.          | semm/m128              |      |          | ssel | 01            | 55   | z P     | 3+            |                                                                     |        |        |           |         |         |          | Bitwise Logical AMD NOT of Packed Single-IP Values           |  |

| ANDPD    | xmm.          | zmm/m128               |      |          | sse2 | 66 01         | 54   | r P     | 4+            |                                                                     |        |        |           |         |         |          | Bitwise Logical AMD of Packed Double-TP Values               |  |

| ANDPS    | xmm.          | zmm/m128               |      |          | ssel | 01            | 54   | z P     | 3+            |                                                                     | 1      |        |           |         |         |          | Bitwise Logical AMD of Packed Single-TP Values               |  |

|          | DARTMENT OF E |                        |      |          |      |               |      |         |               |                                                                     | •      |        | •         |         |         |          | BERKELEY LAN                                                 |  |

### More Wasted Opcodes

|    | CUTPS2PI    | mm.    | xmm/ m6 4 |   |             | _           |      |         |        |          |

|----|-------------|--------|-----------|---|-------------|-------------|------|---------|--------|----------|

|    | CVTSD2SI    | r32/64 | xmm√m64   |   |             |             |      |         |        |          |

|    | CUTSD2SS    | xmm.   | жим√ и 64 |   |             |             |      | FXCH4   | sr     | STi      |

| _  | CUTS123D    | xmm.   | r/m32/64  | _ | r16/32/64   | z/m15/32/64 | _    |         |        |          |

| CM | CUTSI2SS    | житип  | r/m32/64  | - | r16/32/64   | z/m15/32/54 | _    | FXCH4   | sr     | STi      |

| CM |             | житель | 2 Cmm/m32 | i | r16/32/64   | z/m15/32/54 |      | FXCH7   | ST     | STi      |

| CM | CUTSS2SI    | x32/64 | 25mm/m/32 |   | z/n8        | x8          |      | FXCH7   | ST     | STi      |

| CM | P CUTTPD2DQ | xmm.   | xmm/m128  |   | z/m15/32/54 | x16/32/64   |      | FXRSTOR | ST     | SE1      |

| CN | P CUTTPD2PI | тап.   | xmm/m128  |   | r8          | z/m8        |      |         | ST     | STI      |

| CH | P CUTTPS2D0 | xmm.   | xmm/m128  |   | ±16/32/64   | r/m15/32/54 |      | FXRSTOR |        |          |

| -  |             | mm.    | 2020/2054 |   | AL          | inm8        |      | FXSAVE  | m512   | ST       |

|    |             |        |           |   | z AX        | inm16/32    |      | FXSAUE  | m512   | ST       |

| CM | P CUTTSD2SI | x32/64 | xmm√ m6 4 |   | z/m8        | imm0        |      | FXTRACT | sr     |          |

| CM | LCUTTSS2SI  | x32/64 | 20mm/m32  |   | z/m15/32/54 | inm15/32    | _    |         |        | _        |

|    |             | DX     | AX        | - | z/n8        | inge8       |      | FYL2X   | ST1    | ST       |

| CM |             | DX     | AX        | _ | z/m16/32/64 | inmô        | _    | FYL2XP1 | ST1    | ST       |

| CR |             | EDE    | EAX       |   | xnn.        | mm/m128     | inm8 | G3      | GS     |          |

| CM | p CQO       | RDY    | RAX       |   | жил.        | mm/m128     | imm8 | HADDPD  | XCTUT. | xmm/m128 |

| CM | P CMDE      | ERY    | AX        |   |             | m8          |      | HADDPS  | xonon. | xmm/m128 |

| CM | PDAA        | AL     |           |   |             | m 8         |      | HLT     |        |          |

|    |             |        |           |   |             |             |      |         |        |          |

## •We only need 80 out of the nearly 300 ASM instructions in the x86 instruction set!

- •Still have all of the 8087 and 8088 instructions!

- Wide SIMD Doesn't Make Sense with Small Cores

- •Neither does Cache Coherence

- •Neither does HW Divide or Sqrt for loops

- Creates pipeline bubbles

- •Better to unroll it across the loops (like IBM MASS libraries)

- •Move TLB to memory interface because its still too huge (but still get precise exceptions from segmented protection on each core)

INTO eFlags

|                   | Intel<br>Core2<br>(Penryn) | Intel<br>Atom<br>core | Tensilica<br>core w/<br>64-bit FP |

|-------------------|----------------------------|-----------------------|-----------------------------------|

| Die area<br>(mm²) | 53.5                       | 25                    | 5.32                              |

| Process           | 45 nm                      | 45 nm                 | 65 nm                             |

| Power             | 18W                        | 0.625W                | 0.091W                            |

| Freq              | 2930<br>MHz                | 800MHz                | 500MHz                            |

| Flops /<br>Watt   | 162                        | 1280                  | 4065                              |

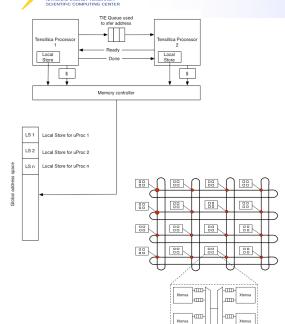

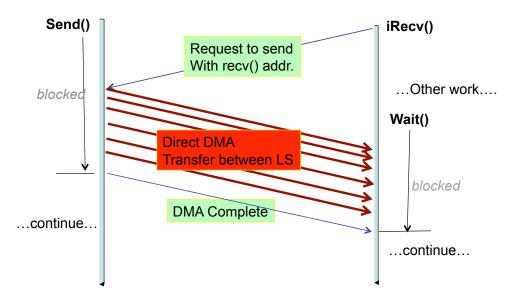

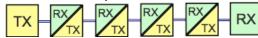

## **Novel Inter-processor Communication**

Direct support for high-level language constructs

- Local Local \$ \$ Memory controller LS 1 Local Store for uProc 1 LS 2 Local Store for uProc 2 **NVRAM** LS n Local Store for uProc n (FLASH) for address fault resilience

- Logical topology is a full

- Each local store mapped to global address space

- To initiate a DMA transfer between processors:

- **Processors exchange starting** addresses through TIE Queue interface

- · Optimized for small transfers

- When ready, copy done directly from

- Copy will bypass cache hierarchy

## **Example Timing Diagram**For MPI-Like 2-sided Message

Office of Green is TIE queue and red is Local Store DMA Engine Science

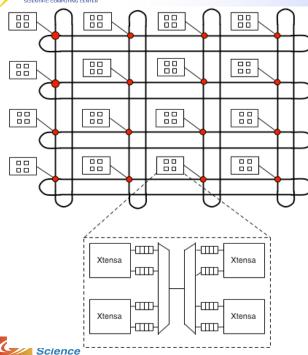

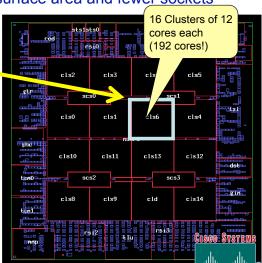

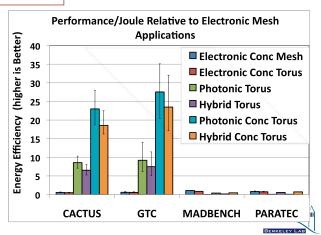

## Network-on-Chip (NoC) Architecture

- Concentrated torus

- Direct connect

between 4

processors on a tile

- Packet switched network connecting tiles

- Between 64 and 128 processors per die

- Silicon Photonics as option for NoC

#### **Fault Resilience**

If you have a 20Million Core System, you should expect some failures

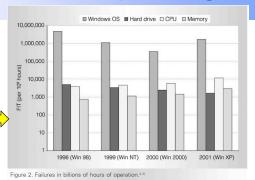

## **Fault Resilience/Checkpointing**

- Industry has strong motivation to keep fault rates per node under control

- Historically target has been to make hardware slightly more reliable than dominant OS (MS Windows)

- Hardening is done in circuit design (transparent to software)

- However, HPC capability has historically grown faster than Moore's law!

- (Moore's law only gets you ~100x in same period)

Therefore, number of nodes increasing (and hence failures)

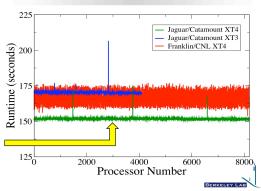

Trault resilience creates 1.50

Trault resilienc

## **Green Flash:**Fault Tolerance/Resilience

- Large scale applications must tolerate node failures

- Our design does not expose unique risks

- Faults proportional to sockets (not cores) & silicon surface area

- Low-power manycore uses less surface area and fewer sockets

#### Hard Errors

- Spare cores in design (Cisco Metro: 188 cores + 8 spares)

- SystemOnChip design (fewer components→fewer sockets)

#### Soft Errors

- ECC for memory and caches

- On-board NVRAM controller for localized checkpoint

32

#### **Software Performance**

Software Auto-tuning: Don't depend on a human to do a machine's job.

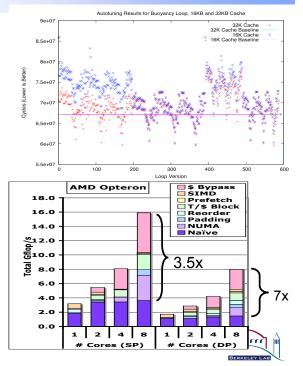

### **Software Auto-tuning**

- Problem: want to compare best potential performance of diverse architectures, avoiding

- Non-portable code

- Labor-intensive user optimizations for each specific architecture

- Our Solution: Auto-tuning

- Automate search across a complex optimization space

- Achieve performance far beyond current compilers

- achieve performance portability for diverse architectures!

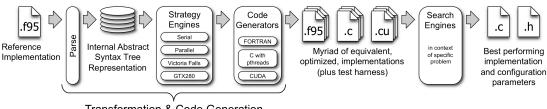

## Generalized Stencil Auto-tuning Framework

- Ability to tune many stencil-like kernels

- No need to write kernel-specific perl scripts

- Uses semantic information from existing Fortran

- Target multiple architectures

- Search over many optimizations for each architecture

- Currently supports multi/manycore, GPUs

- Better performance = Better energy efficiency

Transformation & Code Generation

### **Multi-Targeted Auto-Tuning**

For Performance Portability

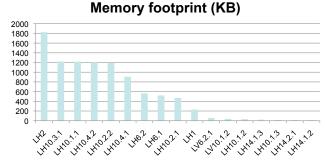

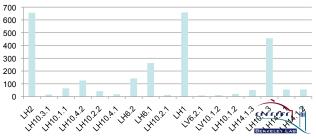

#### **Analyze Climate Code Memory Movement**

NATIONAL ENERGY RESEARCH Optimized Data Movement: Huge Savings in Energy Efficiency and Cost

- Analyzed Each Loop of Climate code Individually

- Trace analysis key to memory requirements

- Actually running the code gives realistic values for memory footprint, temporal reuse, DRAM bandwidth requirements

- Measure DRAM bandwidth for each loop!

- (instruction throughput) X

(memory footprint)/

(instruction counts)

1-byte-per-FLOP could be reduced with local-store

Science

## Bandwidth Requirements (MB/s) (Instructions/Cycle=1, 500 MHz)

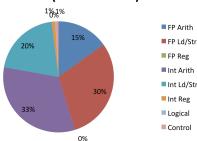

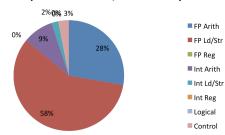

## **Optimizing Instruction Mix**

#### LH2 (small domain)

#### LH2 (small domain, reordered)

- · Memory footprint: 160 KB

- Cache size requirement: 160 KB

- < 50% instructions are floating-point

- Huge overhead for address generation

- Although code streams through data, loop ordering was bad → cachelines reused although addresses were not

- Memory footprint: 160 KB

- Cache size requirement: 1 KB

- > 85% instructions are floating-point

- Good ordering → simpler addressing

160x reduction in cache size! 2x savings in execution time

Science

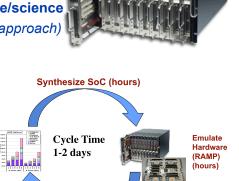

## Rapid Prototyping of System Design

Using RAMP to Accelerate the hardware/software co-design cycle

### **Advanced Hardware Simulation (RAMP)**

**Enabling Hardware/Software/Science Co-Design**

Research Accelerator for Multi-Processors (RAMP)

- Simulate hardware before it is built!

**Design New System**

Cycle Time

4-6+ years

(2 year concept phase)

- Break slow feedback loop for system designs

- Enables tightly coupled hardware/software/science

co-design (not possible using conventional approach)

Build

Hardware

(2 years)

Autotune -

Software

(Hours)

Tune

Software

(2 years)

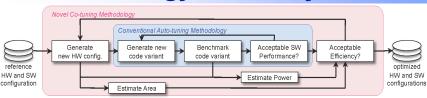

## Hardware/Software Co-Tuning for Energy Efficiency

The approach: Use auto-tuned code when evaluating architecture design points

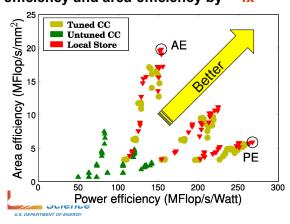

#### Co-Tuning can improve powerefficiency and area-efficiency by ~4x

## Lets Put it All Together!

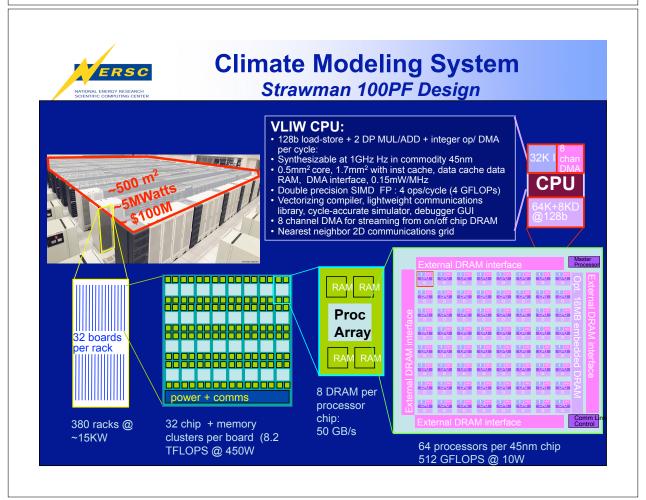

## Strawman Design

# **Green Flash Strawman System Design In 2008**

#### We examined three different approaches:

- AMD Opteron: Commodity approach, lower efficiency for scientific applications offset by cost efficiencies of mass market

- BlueGene: Generic embedded processor core and customize system-on-chip (SoC) services to improve power efficiency for scientific applications

- Tensilica XTensa: Customized embedded CPU w/SoC provides further power efficiency benefits but maintains programmability

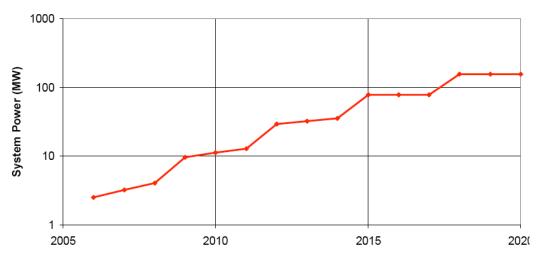

| Processor                         | Clock  | Peak/<br>Core<br>(Gflops) | Cores/<br>Socket | Sockets | Cores | Power  | Cost 2008 |

|-----------------------------------|--------|---------------------------|------------------|---------|-------|--------|-----------|

| AMD Opteron                       | 2.8GHz | 5.6                       | 2                | 890K    | 1.7M  | 179 MW | \$1B+     |

| IBM BG/P                          | 850MHz | 3.4                       | 4                | 740K    | 3.0M  | 20 MW  | \$1B+     |

| Green Flash /<br>Tensilica XTensa | 650MHz | 2.7                       | 32               | 120K    | 4.0M  | 3 MW   | \$75M     |

## **SC08 Green Flash Hardware Demo**

1

- Demonstrated during SC '08

- Proof of concept

- CSU atmospheric model ported to Tensilica Architecture

- Single Tensilica processor running atmospheric model at 50MHz

- Emulation performance advantage

- Processor running at 50MHz vs.

Functional model at 100 kHz

- 500x Speedup

- Actual code running not representative benchmark

Office of Science

## If you Optimize the Processor Then Data Movement Will be the Problem

An "Amdahl's Law" for energy efficient hardware design

# The problem with Wires: Energy to NATIONAL ENERGY RESEARCH MOVE data proportional to distance

- Wire cost to move a bit: (Telegraph Eqn.)

- energy = bitrate \* Length<sup>2</sup> / cross-section area

- On-Chip (1cm): ~1pJ/bit, 100Tb/s

- On-Module (5cm): ~2-5pJ/bit, 10Tb/s

- On-Board (20cm): ~10pJ/bit, 1Tb/s

- Intra-rack (1m): ~10-15pJ/bit, 1Tb/s

- Inter-cabinet(2-50m): 15-30pJ/bit, 5-10Tb/s aggregate

- To move a bit with optics: target ~1-2pJ/bit for all distance scales

Photonics requires no redrive and passive switch little power

Copper requires to signal amplification even for on-chip connections

## Silicon Photonics for Energy-Efficient Communication

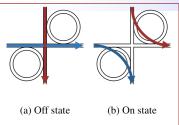

Silicon Photonic Ring Resonator

- Silicon photonics enables optics to be integrated with conventional CMOS

- Enables up to 27x improvement in communication energy efficiency!

of environment at all scales

### **Summary**

- Power is leading design constraint for future HPC

- Future technology driven by handheld space

- Notion of "commodity" moving on-chip

- Approach for Power Efficient HPC

- Choose the science target first (climate in this case)

- **Design systems for applications** (rather than the reverse)

- Design hardware, software, scientific algorithms together using hardware emulation and auto-tuning

- This is the right way to design efficient HPC systems!

## **Acknowledgements**

#### **Students**

- Marghoob Mohiyuddin

- Shoaib Kamil

- Jens Krueger

- Kaushik Datta

- Kamesh Madurri

- Cy Chan

#### Staff

- David Donofrio

- Leonid Oliker

- Michael Wehner

- Tony Drummond

- Woo-Sun Yang

- Norman Miller

- Sam Williams

#### **More Info**

- Green Flash

- http://www.lbl.gov/CS/html/greenflash.html

- NERSC System Architecture Group

- http://www.nersc.gov/projects/SDSA

- The Berkeley View/Parlab

- http://view.eecs.berkeley.edu

- http://parlab.eecs.berkeley.edu/

- LBNL Future Technologies Group

## Mitigating Cost of Verification and Defects: Cisco CRS-1 Terabit Router

188+4 Xtensa general purpose processor cores per Silicon Packet Processor Up to 400,000 processors per system

• (this is not just about HPC!!!)

Replaces ASIC using 188 GP cores! Emulates ASIC at competitive power/performance

Better power/performance than FPGA! New Definition for "Custom" in SoC