# Optimizing 27-point Stencil on Multicore

Kaushik Datta, Samuel Williams, Vasily Volkov, <u>Jonathan Carter</u>, Leonid Oliker, John Shalf, and Katherine Yelick CRD/NERSC, Berkeley Lab

**EECS**, University of California, Berkeley

JTCarter@lbl.gov

iWAPT 2009 October 1-2 2009

# **Expanding Set of Manycore Architectures**

- Potential to deliver most performance for space and power for HPC

- Server and PC commodity

- Intel and AMD x86, Sun UltraSparc

- Graphics Processors& Gaming

- NVIDIA GTX280, STI Cell

- Embedded

- Intel Atom, ARM (cell phone, etc.)

Picochip DSP 1 GPP core 248 ASPs

STI Cell 8 ASPs, 1GPP

Cisco CRS-1 188 Tensilica GPPs

Sun Niagara 8 GPP cores (32 threads)

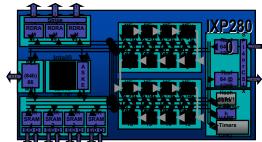

Intel Network Processor

1 GPP Core

16 ASPs (128 threads)

### **Auto-tuning**

Problem: want to obtain and compare best potential performance of diverse architectures, avoiding

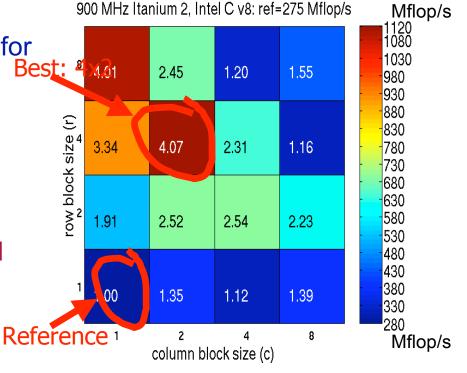

For finite element problem (BCSR) [Im, Yelick, Vuduc, 2005]

Non-portable code

Labor-intensive user optimizations for each specific architecture

- Automate search across a complex optimization space

- Achieve performance far beyond current compilers

- Achieve performance portability for diverse architectures

# Maximizing In-core Performance

- •Exploit in-core parallelism (ILP, DLP, etc...)

- Good (enough)floating-point balance

# reorder unroll & jam eliminate explicit SIMD

#### Maximizing Memory Bandwidth

- Exploit NUMA

- Hide memory latency

- Satisfy Little's Law

# unit-stride streams memory affinity SW prefetch DMA IIsts blocking

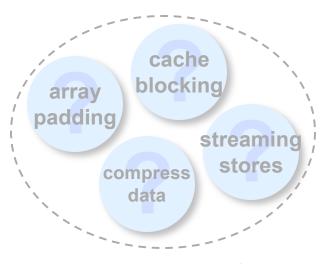

# Minimizing Memory Traffic

- Capacity misses

- Conflict misses

- Compulsory misses

- Write allocate behavior

## Maximizing In-core Performance

- •Exploit in-core parallelism (ILP, DLP, etc...)

- Good (enough) floating-point balance

# reorder / unroll & jam eliminate explicit branches SIMD

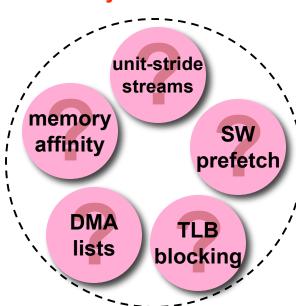

#### Maximizing Memory Bandwidth

- Exploit NUMA

- Hide memory latency

- Satisfy Little's Law

# Minimizing Memory Traffic

- Capacity misses

- Conflict misses

- Compulsory misses

- Write allocate behavior

## Maximizing In-core Performance

- •Exploit in-core parallelism (ILP, DLP, etc...)

- Good (enough)floating-point balance

# reorder / unroll & jam eliminate explicit branches SIMD

#### Maximizing Memory Bandwidth

- Exploit NUMA

- Hide memory latency

- Satisfy Little's Law

# unit-stride streams memory affinity SW prefetch DMA IIsts blocking

# Minimizing Memory Traffic

- Capacity misses

- Conflict misses

- Compulsory misses

- Write allocate behavior

## Maximizing In-core Performance

- •Exploit in-core parallelism (ILP, DLP, etc...)

- Good (enough) floating-point balance

# reorder unroll & jam eliminate explicit branches

#### Maximizing Memory Bandwidth

- Exploit NUMA

- Hide memory latency

- Satisfy Little's Law

# unit-stride streams memory affinity SW prefetch DMA TLB blocking

# Minimizing Memory Traffic

- Capacity misses

- Conflict misses

- Compulsory misses

- Write allocate behavior

#### Maximizing **In-core Performance**

Exploit NUMA

**Maximizing Memory Bandwidth**

**Minimizing Memory Traffic**

Exploit in-core parallelism (ILP, DLP, etc...)

eliminate

Good (enough) floating-point balance

explicit

streams

memory

DMA lists

TLB blocking inate: acity misses

onflict misses

**Sory misses**

allocate behavior

unroll &

jam

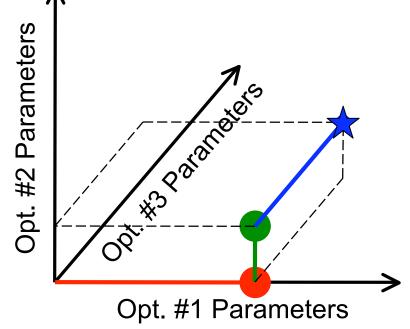

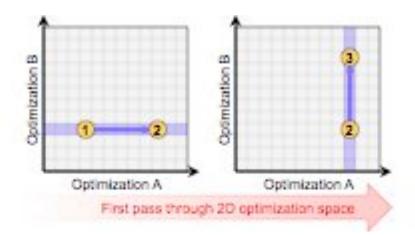

#### **Traversing the Parameter Space**

- Exhaustive search of these complex layered optimizations is impossible

- To make problem tractable, we:

- order the optimizations

- applied them consecutively

Every platform had its own set of best parameters

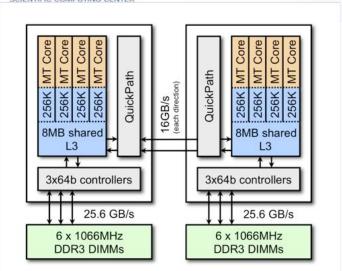

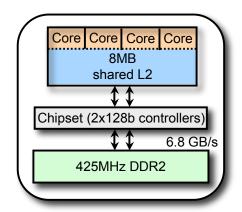

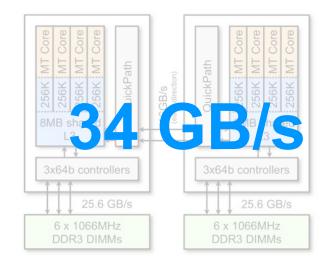

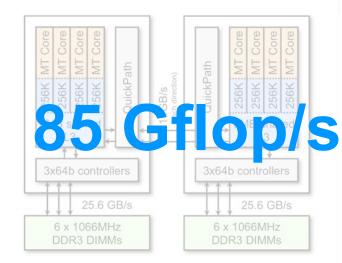

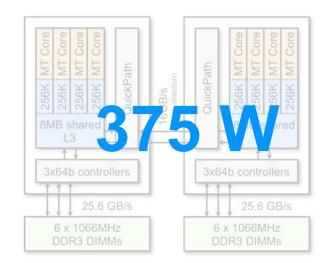

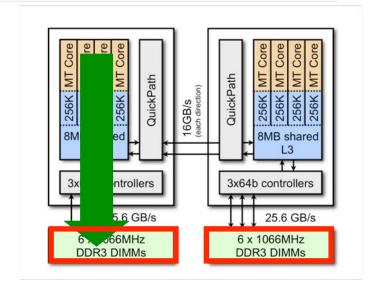

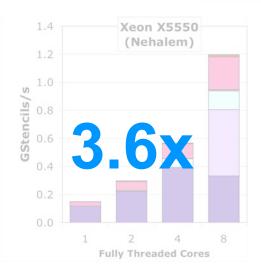

#### Intel Nehalem (Gainestown)

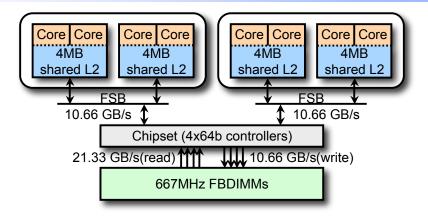

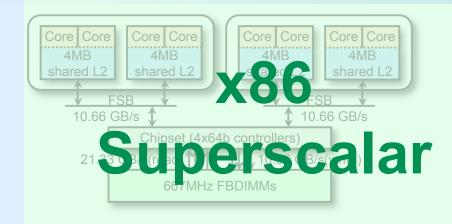

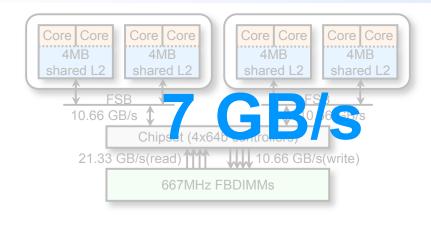

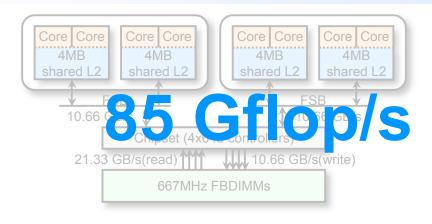

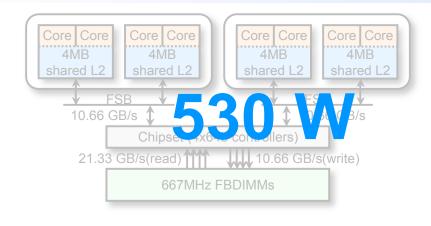

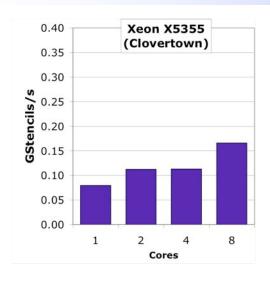

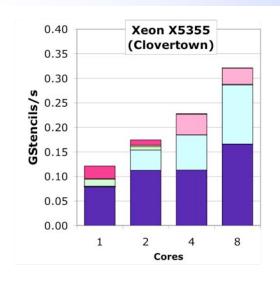

#### Intel Clovertown

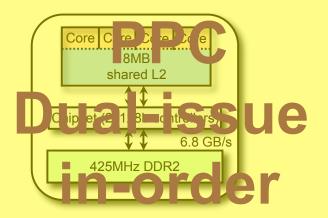

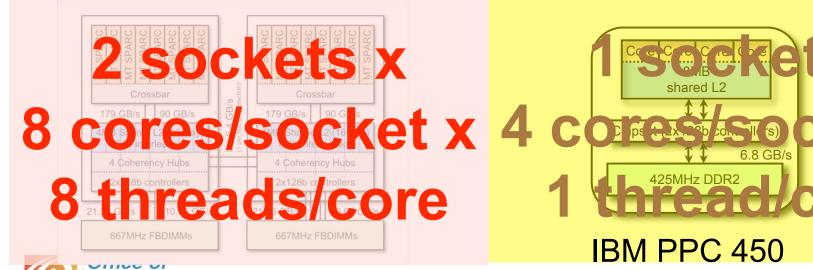

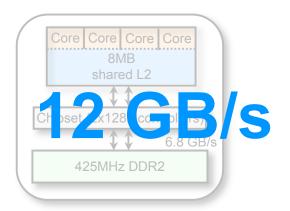

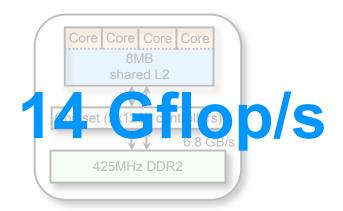

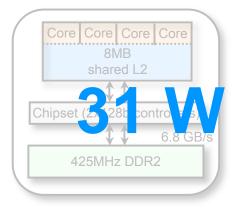

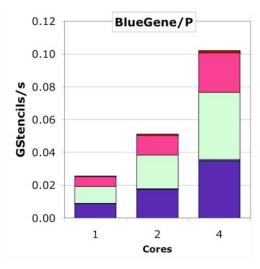

IBM PPC 450 (BG/P)

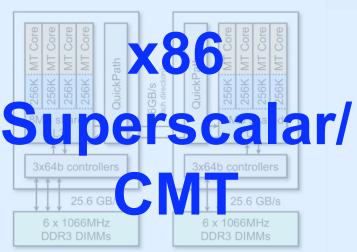

#### Intel Nehalem (Gainestown)

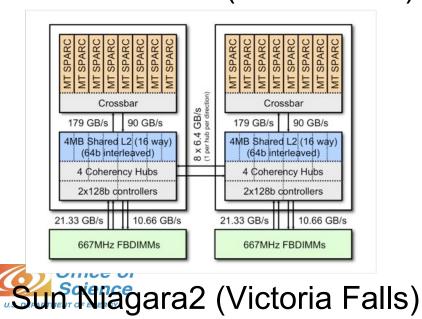

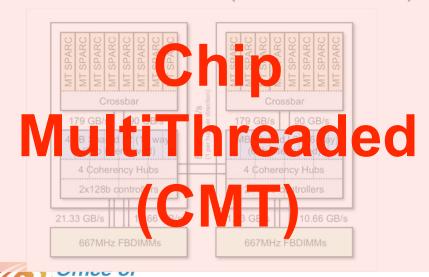

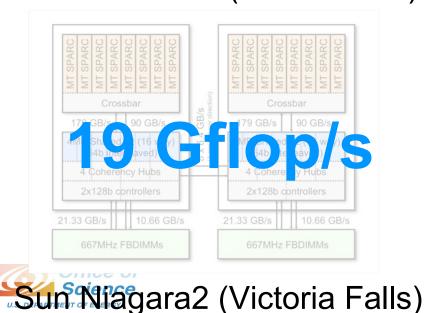

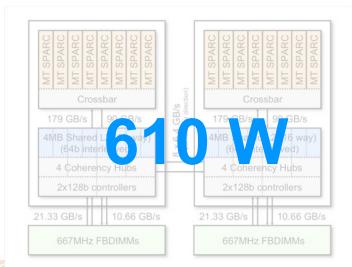

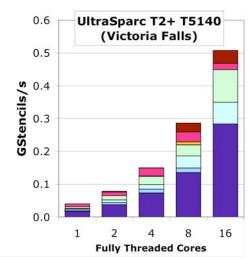

Sun Niagara2 (Victoria Falls)

Intel Clovertown

IBM PPC 450 (BG/P)

Co Corp. Cor thread/core

rrrrrr

Intel Nehalem (Gainestown)

Miagara2 (Victoria Falls)

Intel Clovertown

(BG/P)

#### Intel Nehalem (Gainestown)

Sun Niagara2 (Victoria Falls)

#### Intel Clovertown

IBM PPC 450 (BG/P)

#### Intel Nehalem (Gainestown)

#### Intel Clovertown

IBM PPC 450 (BG/P)

#### Intel Nehalem (Gainestown)

#### Intel Clovertown

IBM PPC 450 (BG/P)

Sun Magara2 (Victoria Falls)

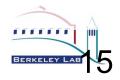

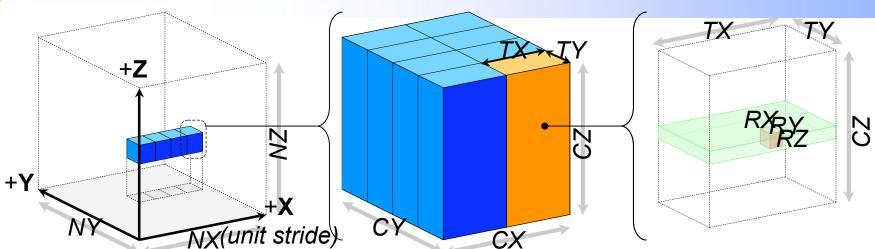

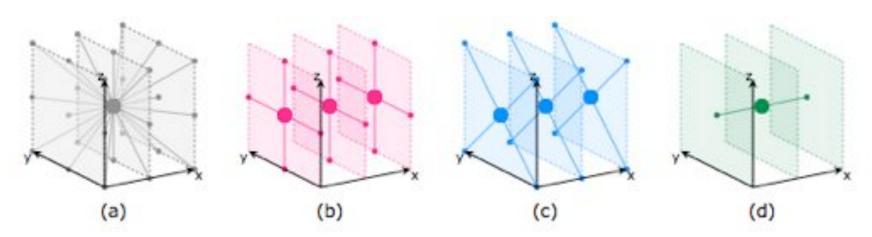

#### **Stencil Code Overview**

- For a given point, a stencil is a fixed subset of nearest neighbors

- A stencil code updates every point in a regular grid by "applying a stencil"

- Used in iterative PDE solvers like Jacobi, Multigrid, and AMR

- Focus on a out-of-place 3D 27point stencil sweeping over a 256<sup>3</sup> grid

- Problem size > Cache size

- Stencil codes characteristics

- Long unit-stride memory accesses

- Some reuse of each grid point

- 30 flops per grid point

S. DEPARTMENT OF ENERGY

Adaptive Mesh Refinement (AMR)

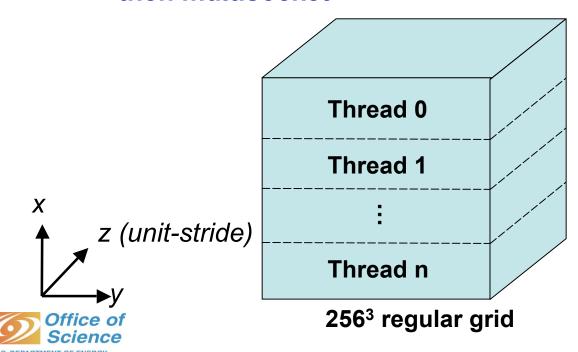

#### **Naïve Stencil Code**

- We wish to exploit multicore resources

- Simple parallel stencil code:

- Use pthreads

- Parallelize in least contiguous grid dimension

- Thread affinity for scaling: multithreading, then multicore, then multisocket

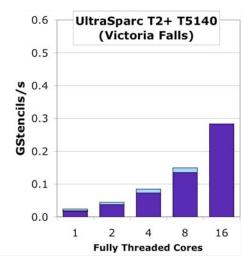

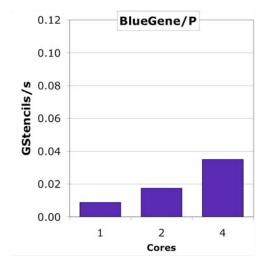

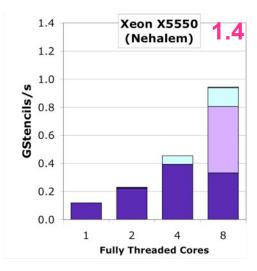

#### **Naïve Performance**

- Compiler delivers poor performance

- icc for Intel

- gcc for VF

- xlc for BG/P

- No parallel scaling for two architectures

- Low performance as compared with stream bandwidth prediction

- Reasonably high

Al means that

other bottlenecks

likely exist

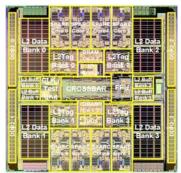

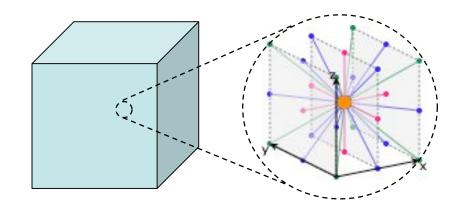

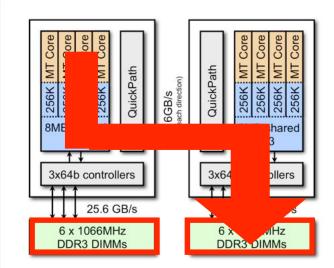

#### **NUMA Optimization**

- All DRAMs are highlighted in red

- Co-located data on same socket as thread processing it

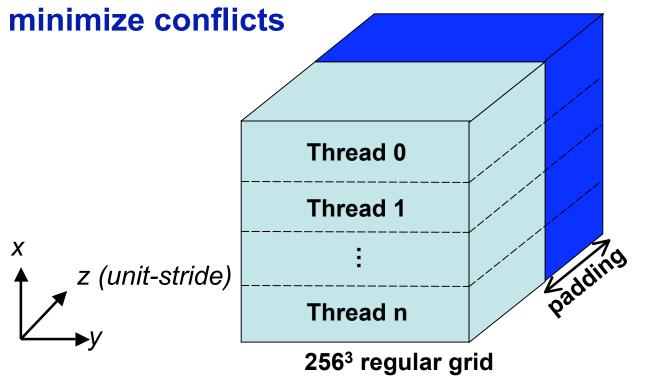

#### **Array Padding Optimization**

Conflict misses may occur on low-associativity caches

Each array was padded by a tuned amount to

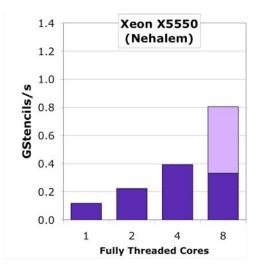

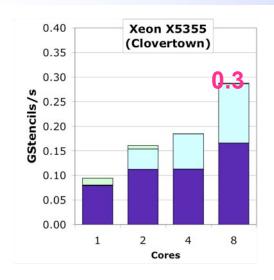

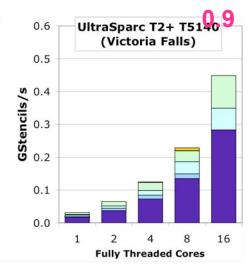

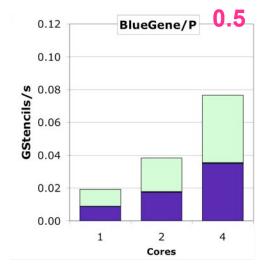

#### **Performance**

+ Array Padding

+ NUMA

Naive

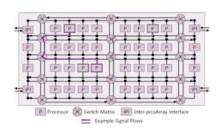

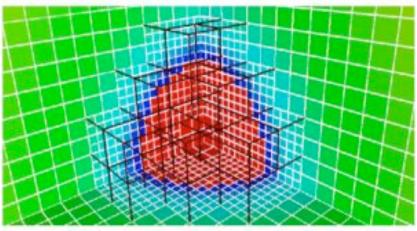

#### **Problem Decomposition**

## **Decomposition of the Grid** into a Chunk of Core Blocks

- Large chunks enable efficient NUMA Allocation

- Small chunks exploit LLC shared caches

## Decomposition into Thread Blocks

Exploit caches shared among threads within a core

#### Decomposition into Register Blocks

- Make DLP/ILP explicit

- Make register reuse explicit

- This decomposition is universal across all examined architectures

- Decomposition does not change data structure

- Need to choose best block sizes for each hierarchy level

#### **Performance**

- + Thread Blocking

- □ + Register Blocking

- + Core Blocking

- + Array Padding

- + NUMA

- Naive

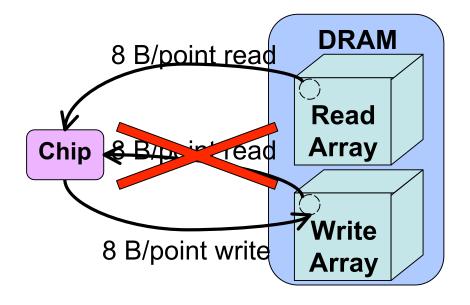

#### **ISA Specific Optimizations**

- Software prefetch

- Explicit SIMD

- PPC SIMD loads do not improve performance due to unaligned data

- Cache Bypass

- Initial values in write array not used

- Eliminate write array cache fills with intrinsics

- Reduces memory traffic from 24 B/point to 16 B/point

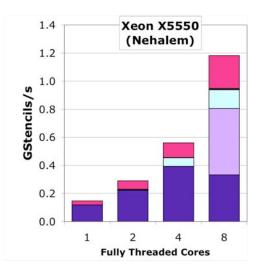

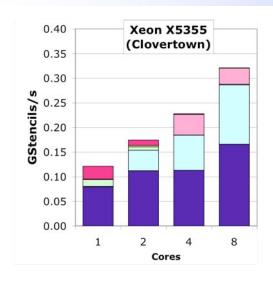

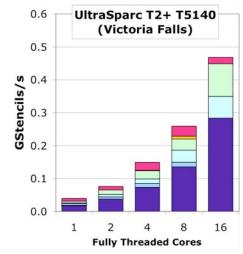

#### **Performance**

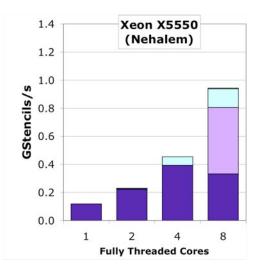

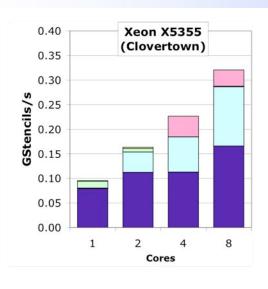

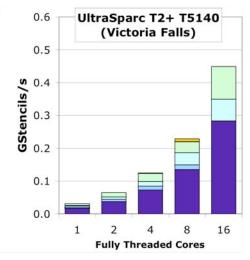

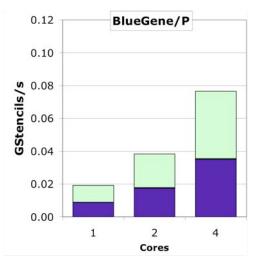

Optimizations effect architectures in different ways

- + SIMD

- + Software Prefetch

- + Thread Blocking

- ☐ + Register Blocking

- + Core Blocking

- + Array Padding

- + NUMA

- Naive

# **Common Subexpression Elimination Optimization**

- Common computation exists between different stencil updates

- Compiler does not recognize this

- Reduce number of flops from 30 to 18

#### **CSE Version Performance**

- + CSE

- + Cache Bypass

- + SIMD

- + Software Prefetch

- + Thread Blocking

- ☐ + Register Blocking

- + Core Blocking

- + Array Padding

- + NUMA

- Naive

#### Is Performance Acceptable?

- A model (e.g. Roofline) could be used to predict best performance

- Use a two-pass greedy algorithm

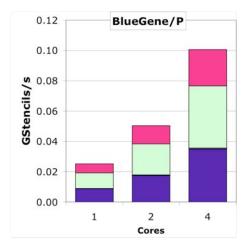

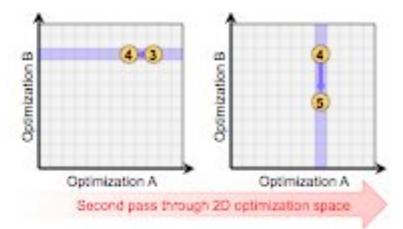

#### **Second Pass Performance**

- + Second Pass

- + CSE

- + Cache Bypass

- + SIMD

- + Software Prefetch

- + Thread Blocking

- ☐ + Register Blocking

- + Core Blocking

- + Array Padding

- + NUMA

- Naive

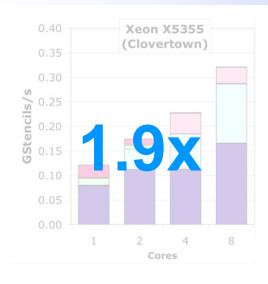

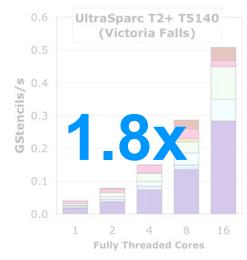

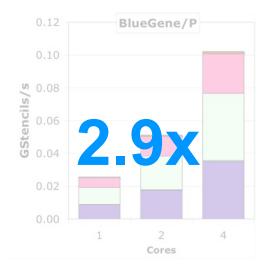

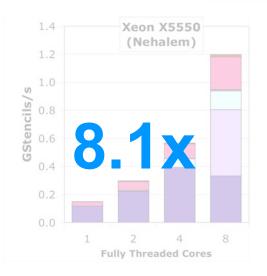

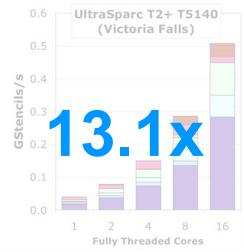

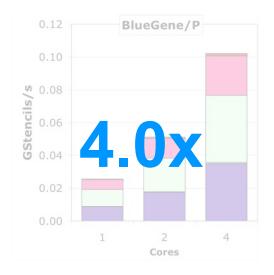

#### **Tuning Speedup**

Speedup at maximum concurrency

#### **Parallel Speedup**

- Speedup going from a single core to maximum concurrency

- All architectures now scale

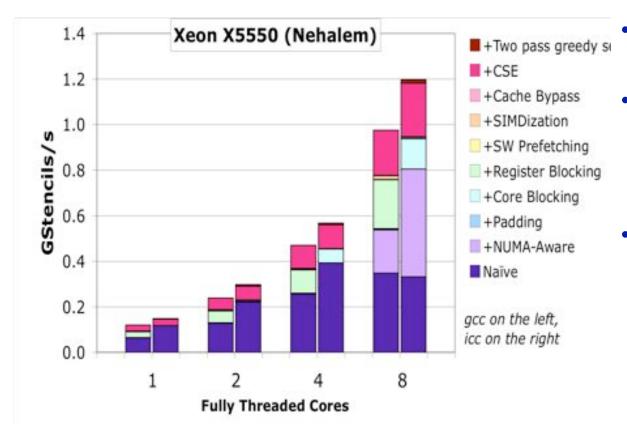

#### **Effect of compilers**

- icc is consistently better than gcc

- For single socket gcc + register blocking has equivalent performance to icc

- Core blocking improves icc performance, but not gcc

- Inferior code generation hides memory bottleneck?

U.S. DEPARTMENT OF ENERGY

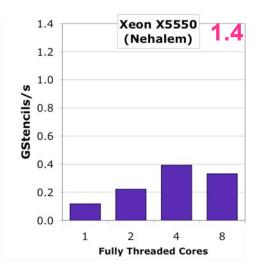

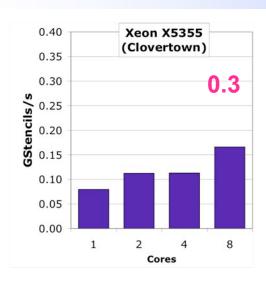

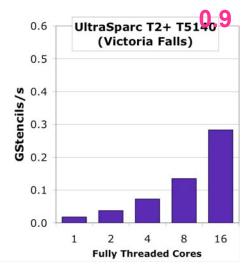

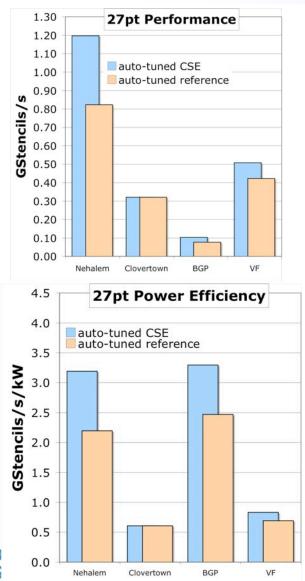

#### **Performance Comparison**

- Intel Nehalem best in absolute performance

- Normalize for low power, BG/P solution is much more attractive

#### **Conclusions**

- Compiler alone achieves poor performance

- Low fraction possible performance

- Often no parallel scaling

- Autotuning is essential to achieving good performance

- 1.8x-3.6x speedups across diverse architectures

- Automatic tuning is necessary for scalability

- Most optimization with the same code base

- Clovertown required SIMD (hampers productivity) for best performance

- When power consumption is taken into account, BG/P performs well

#### Acknowledgements

- UC Berkeley

- RADLab Cluster (Nehalem)

- PSI cluster(Clovertown)

- Sun Microsystems

- Niagara2 donations

- ASCR Office in the DOE Office of Science

- contract DE-AC02-05CH11231